We thought some of you may enjoy seeing some behind-the-scenes action, so I’m going to try to post more on that topic.

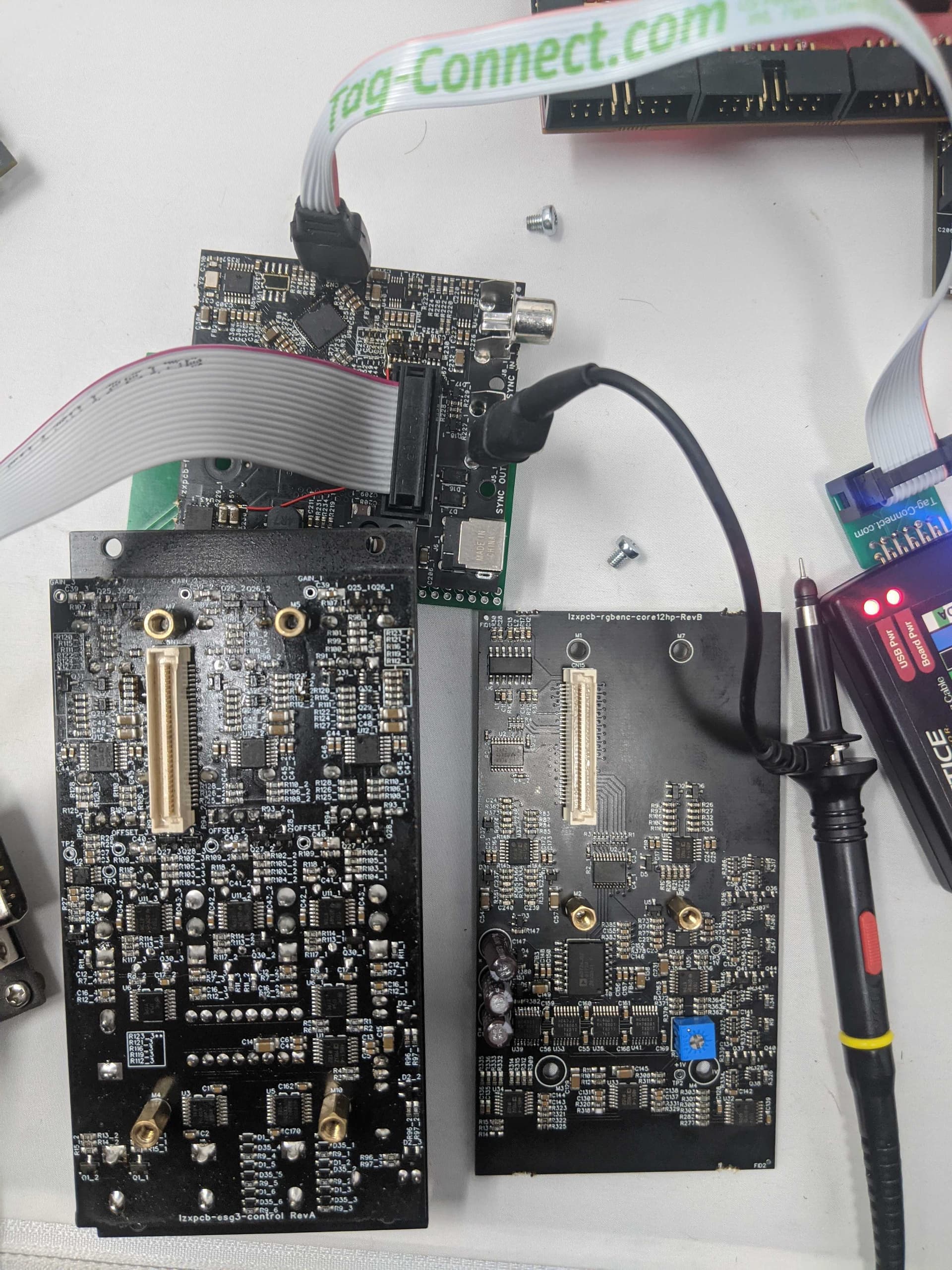

Today we reviewed a new PCB that came in last week, lzxpcb-fpga12hp-RevA The workshop team built 5 of these up yesterday. This is the third “outer layer” variant for Gen3, and is a general purpose power entry and FPGA subsystem PCBA. The first two modules that will use this assembly include ESG3 and DSG3.

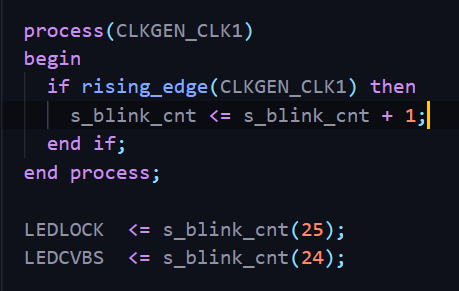

This board is similar to our existing power entry + sync separator board (p/n lzxpcb-sync12), but adds an HD/SD Clock Generator and a small Lattice ICE5 series FPGA. In ESG3, this FPGA’s firmware is responsible for everything related to generating the timing of the video encoder’s outputs.

Another feature we like on this board is the Tag-Connect programmer footprint! We finally decided to give these spring-loaded pin cables a go since our footprint demands were so small on this board.

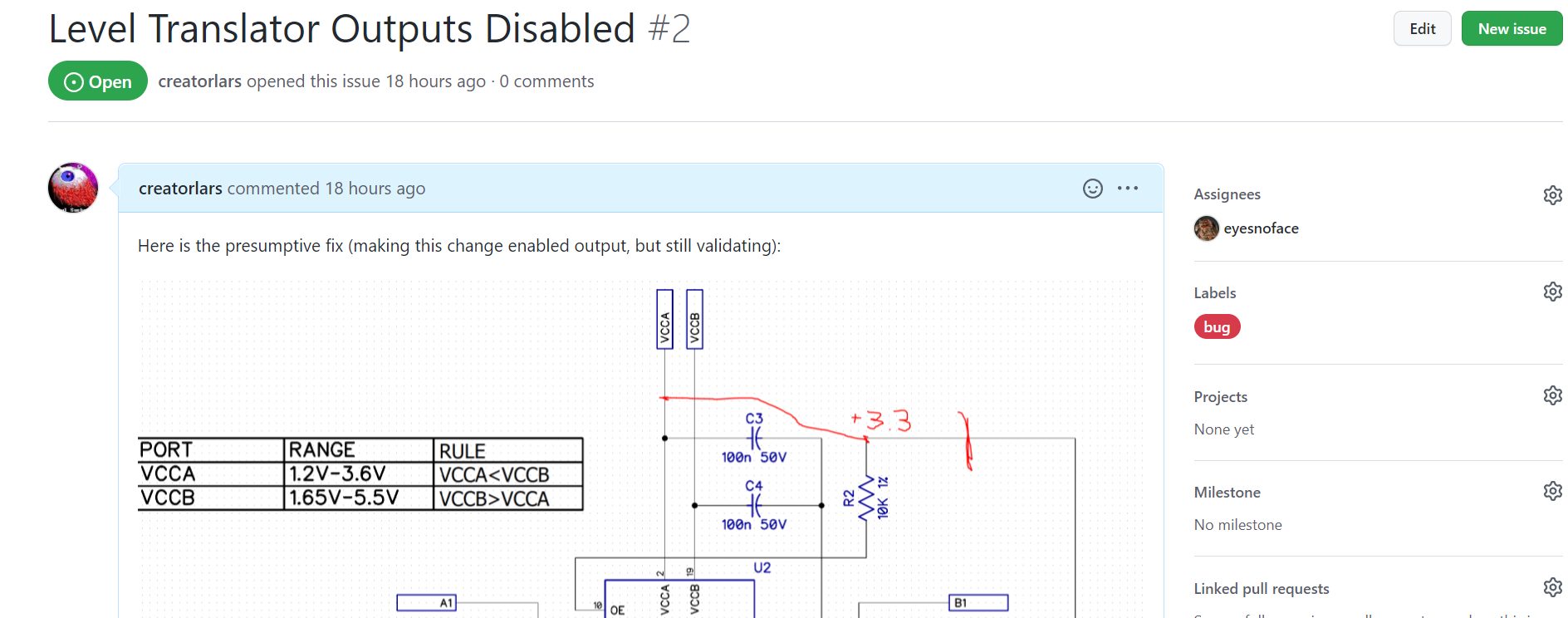

At the end of the day we’ve got our test articles all powering up, with firmware uploading successfully! With this confirmed, tomorrow we move on to testing our other new review board this week: lzxpcb-esg3-core. If that one looks good, we’ll be one big step closer to greenlighting this project.

Here’s the earlier esg3 prototype, showing our first approach (which had the FPGA on the core assembly instead of the upper power entry board.)

I hope you enjoyed seeing some process photos, let us know if you want to see more of this kind of thing, and if so, what parts of the process you like seeing most.

Always a pleasure getting a look behind the scenes and nerd out over some PCB design

Always a pleasure getting a look behind the scenes and nerd out over some PCB design